| TITLE: H | FITLE: Education |             |  |

|----------|------------------|-------------|--|

|          | Revisin          | V0.1        |  |

| Status   | Date             | 2015 /05/25 |  |

|          | Doc              | LK임베디드      |  |

# 자일링스 FPGA 개발모듈 매뉴얼 (LK-FPGA-XC3 Manual)

이경남

LK임베디드

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | LK임베디드      |

| LK Development Team |  |  |

|---------------------|--|--|

| K EMBEDDED          |  |  |

### 1.제품소개 및 특징

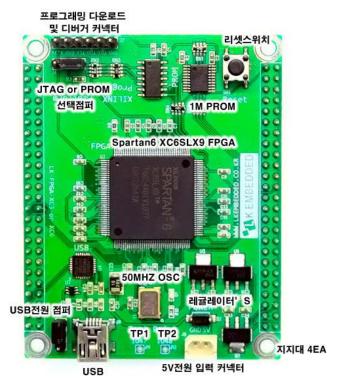

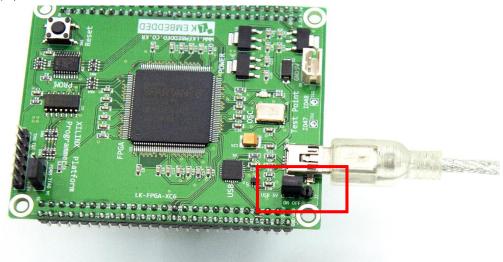

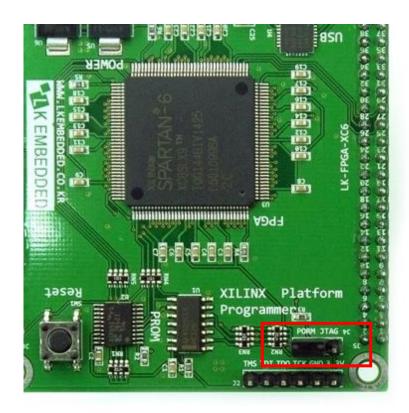

<그림 1.1> LK-FPGA-XC3 개발모듈 사진

#### 1.1 제품소개

#### FPGA란?

FPGA는 Field Programmable Gate Array의 약어로서, 디지털 회로의 논리소자를 프로그램으로 쉽게 구성할 수 있는 반도체이다. 미리 구축된 로직블록 및 프로그래밍 가능한 라우팅 리소스가 직접 하드웨어를 부품 하나하나 설계를 하지 않아도 필요한 기능구현을 위한 칩을 구성 할 수 있다. 또한 FPGA는 완벽하게 하드웨어의 재구성이 가능하며, 다른 회로 구성을 설계하고 재 컴파일 하면 바로 새로운 기능을 하는 하드웨어 구성이 된다. 또한 FPGA는 완벽하게 하드웨어의 재구성이 가능하며, 다른 회로구성을 설계하고 재 컴파일 하면 바로 새로운 기능을 하는 하드웨어 필하면 바로 새로운 기능을 하는 하드웨어 필다. 즉, 프로그램으로 쉽게 바꿀 수 있는 하드웨어로 볼 수 있다. FPGA는 전기전인 퓨즈에 의한 사용자 프로그래밍으로 원하는 사용자 회로를 빠른 시간에 구현할 수 있게 해준다. 또한 유연성 있는 논리 및 연결구조로 인하여 고성능의 회로를 구현할 수 있게 한다.

| TITLE: Education |         |             |  |  |

|------------------|---------|-------------|--|--|

|                  | Revisin | V0.1        |  |  |

| Status           | Date    | 2015 /05/25 |  |  |

|                  | Doc     | LK이베디드      |  |  |

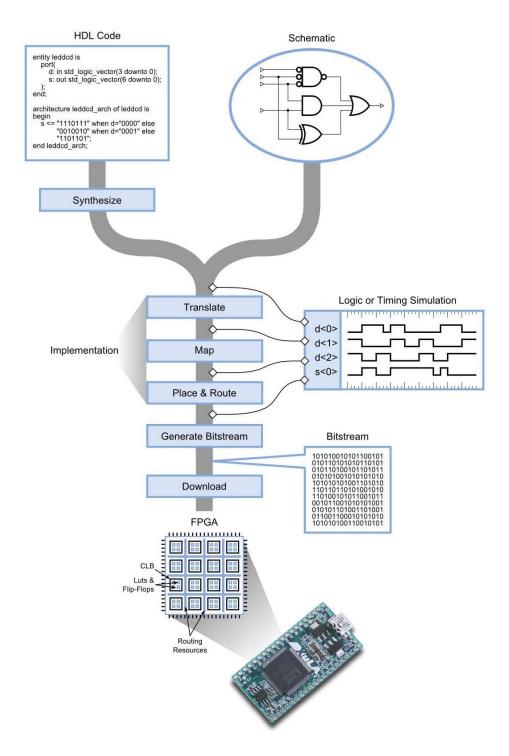

<그림 1.2> FPGA 합성 Flow

Logic Block에는 디지털 회로를 구현할 수 있는 게이트, Flip-Flp, 멀티플렉서 등이 배치되어 있다. I/O Block에는 입력 및 출력회로의 용도에 맞게 구성하기 위한 회로들이 외부 핀과 함께 배치되어 있다. 또한 FPGA는 Array Based와 Row Based 두 가지 방법이 있으며, 구조는 Gate Array와 매우 흡사하지만 Program에 의해 내부 회로 배선이 연결되는 형식을 취하고 있다. FPGA는 Logic Cell 위주의 설계 방식이기 때문에 SPLD Block 내부의 배선이 외부와 직접 연결될 수 있도록 고안되어 있어 일반 Gate Array와 매우비슷하며 타이밍 시뮬레이션(Timming simulation)이 반드시 필요하다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | LK임베디드      |

#### 자일링스 FPGA개발모듈에 내장된 Sprtan3 XC3S200이란?

자일링스(Xilinx)社의 FPGA Sprtan-3 계열의 고용량, 저비용의 전자시스템에 적합하도록 설계되어 나온 제품이다. 총 8가지 종류로 나누어져 있으며, 로직셀은 1,728 ~ 74,880개로 구성되어 있고, 시스템 게이트 수는 50,000~5,000,000개로 구성되었다.

이전 제품인 Sprtan-IIE 패밀리보다 향상된 소비전력, 증가 된 로직 셀과 내부 Block Ram의 용량, I/O 개수 증가, 개선 된 클럭 관리 기능, DDR SDRAM memory controller를 가지고 있어 더욱 넓은 활용 범위를 가지고 있으면, 가격 또한 이전 버전의 계열보다 저렴해 졌다. Spartan-3 계열의 발전된 프로세서 기술을 사용한 향상된 기능들은 프로그램이 가능한 로직 프로세서 산업에 있어서 FPGA의 새로운 표준을 제시하고 있다. 이러한 고효율 및 적은비용 때문에 Sprtan-3 계열의 FPGA는 통신, 가전제품, 영상처리, 신호처리 등을 사용하는 여러 제품에 사용 되고 있다. 또한 주문형 반도체인 ASIC을 대체 할 수 있는 획기적인 솔루션으로 각광을 받고 있다 아래 표에서 자일링스(Xilinx)社의 Spartan-3계열의 각각의 특징 및 사이즈를 확인 할 수 있다.

Table 1: Summary of Spartan-3 FPGA Attributes

| Device System Equivalent | (One  | CLB Array<br>One CLB = Four Slices) |      | Block<br>RAM Bits | Dedicated     | DCMs                 | Max.   | Maximum<br>Differential |        |          |           |

|--------------------------|-------|-------------------------------------|------|-------------------|---------------|----------------------|--------|-------------------------|--------|----------|-----------|

| Device                   | Gates | Logic Cells <sup>(1)</sup>          | Rows | Columns           | Total<br>CLBs | RAM Bits<br>(K=1024) |        | Multipliers             | DCIVIS | User I/O | I/O Pairs |

| XC3S50 <sup>(2)</sup>    | 50K   | 1,728                               | 16   | 12                | 192           | 12K                  | 72K    | 4                       | 2      | 124      | 56        |

| XC3S200 <sup>(2)</sup>   | 200K  | 4,320                               | 24   | 20                | 480           | 30K                  | 216K   | 12                      | 4      | 173      | 76        |

| XC3S400 <sup>(2)</sup>   | 400K  | 8,064                               | 32   | 28                | 896           | 56K                  | 288K   | 16                      | 4      | 264      | 116       |

| XC3S1000 <sup>(2)</sup>  | 1M    | 17,280                              | 48   | 40                | 1,920         | 120K                 | 432K   | 24                      | 4      | 391      | 175       |

| XC3S1500                 | 1.5M  | 29,952                              | 64   | 52                | 3,328         | 208K                 | 576K   | 32                      | 4      | 487      | 221       |

| XC3S2000                 | 2M    | 46,080                              | 80   | 64                | 5,120         | 320K                 | 720K   | 40                      | 4      | 565      | 270       |

| XC3S4000                 | 4M    | 62,208                              | 96   | 72                | 6,912         | 432K                 | 1,728K | 96                      | 4      | 633      | 300       |

| XC3S5000                 | 5M    | 74,880                              | 104  | 80                | 8,320         | 520K                 | 1,872K | 104                     | 4      | 633      | 300       |

#### Notes:

- 1. Logic Cell = 4-input Look-Up Table (LUT) plus a 'D' flip-flop. "Equivalent Logic Cells" equals "Total CLBs" x 8 Logic Cells/CLB x 1.125 effectiveness.

- 2. These devices are available in Xilinx Automotive versions as described in DS314: Spartan-3 Automotive XA FPGA Family.

<표 1.1> Xilinx社의 Sprtan-3 Attributes(속성)

#### 1.2 제품특징

- 1) 자일링스사의 Spartan3 Family, XC3S200 FPGA 내장

- 2) 91개의 I/O(입출력)핀을 2개의 핀 헤더 커넥터(2.54)와 연결

- 3) 3가지 동작전압 제공(1.2V, 2.5V, 3.3V 레귤레이터), 2P 몰렉스 커넥터 내장(외부 입력전원 5V)

- 4) 1Mbits에 통신속도를 제공하는 USB통신 IC내장, 점퍼 설정을 통한 USB전원 5V 선택 가능

- 5) 프로그래밍 가능한 1M Configuration PROM 내장

- 6) 50Mhz 오실레이터, 리셋스위치, IDLE LED 내장, 2개의 TP I/O(테스트 포인트) 제공

- 7) 자일링스 USB 프로래머 이용하여 다운로드 및 디버깅 가능, JTAG 및 PROM 모드 설정 가능

- 8) 사용자 매뉴얼 제공 및 예제코드 제공

| TITLE: Education |         |             |  |  |

|------------------|---------|-------------|--|--|

|                  | Revisin | V0.1        |  |  |

| Status           | Date    | 2015 /05/25 |  |  |

|                  | Doc     | LK임베디드      |  |  |

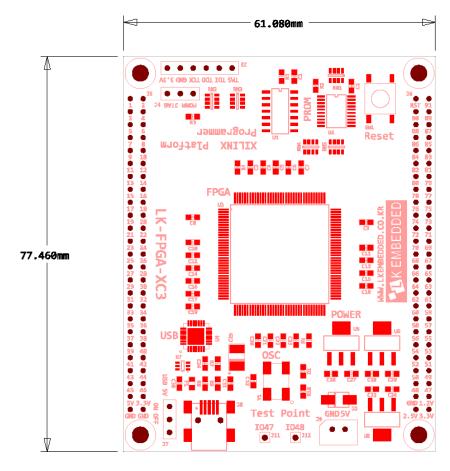

<그림 1.3> LK-FPGA-XC3 개발모듈 구성

<그림 1.4> LK-FPGA-XC3 개발모듈 외형 치수(PCB Dimension)

| TITLE: | Е | ducation |             |

|--------|---|----------|-------------|

|        |   | Revisin  | V0.1        |

| Status |   | Date     | 2015 /05/25 |

|        |   | Doc      | IK이베디드      |

| LK Development Team |  |  |

|---------------------|--|--|

| K EMBEDDED          |  |  |

#### 1.3 커넥터 정보

#### 1) 2x25 핀 헤더 커넥터 핀 배치

| J5 2X25_PINI | HEADER                                                                                                                                                                                                              | J6 2X25                                                                                                                                                                                                                                                       | 5_PINHEADER                                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IO_1         | 2 10_2 4 10_4 6 10_6 8 10_8 10 10_10 12 10_12 14 10_14 16 10_16 18 10_18 20 10_20 22 10_22 24 10_24 26 10_26 28 10_28 30 10_30 32 10_32 34 10_34 36 10_36 38 10_38 40 10_40 42 10_42 44 10_44 46 10_46 48 3.3V_DVDD | RESET 1  IO 90 3  IO 88 5  IO 86 7  IO 82 11  IO 80 13  IO 76 17  IO 74 19  IO 72 21  IO 70 23  IO 68 25  IO 66 27  IO 64 29  IO 62 31  IO 63 33  IO 58 35  IO 56 37  IO 54 39  IO 52 41  IO 50 43  IO 50 43  IO 54 39  IO 52 41  IO 50 43  IO 54 45  GNID 47 | 2 IO_91 4 IO_89 6 IO_87 8 IO_85 10 IO_83 12 IO_81 14 IO_79 16 IO_77 18 IO_75 20 IO_73 22 IO_71 24 IO_69 26 IO_67 28 IO_65 30 IO_63 32 IO_61 34 IO_59 36 IO_57 38 IO_55 40 IO_53 42 IO_51 44 IO_49 46 IO_47 48 I.2V_DVDD |

| GND 49       | 50 GND                                                                                                                                                                                                              | 2.5V_DVDD 49                                                                                                                                                                                                                                                  | 50 3.3V_DVDD                                                                                                                                                                                                            |

<그림 1.5> 핀 헤더(2.54mm Pitch) 커넥터

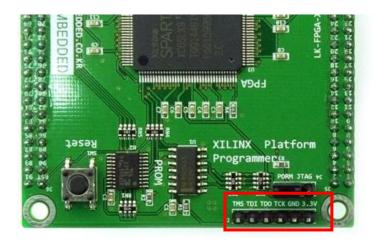

#### 2) 1x6 핀 헤더 커넥터 핀 배치

<그림 1.6> 프로그래밍 다운로드 및 디버거 핀 헤더 커넥터

| 1    | 2    | 3    | 4    | 5    | 6    |

|------|------|------|------|------|------|

| 3.3V | DGND | XTCK | XTDO | XTDI | XTMS |

〈표 1.2〉 프로그래밍 다운로드 및 디버거 핀 배열

| TITLE: E | ducation |             |

|----------|----------|-------------|

|          | Revisin  | V0.1        |

| Status   | Date     | 2015 /05/25 |

|          | Doc      | LK임베디드      |

| LK Development Team |     |  |

|---------------------|-----|--|

| K EMBEDI            | DED |  |

#### 3) USB 커넥터

<그림 1.7> USB 전원(사용 여부) 설정 점퍼

점퍼 설정을 통하여USB전원 사용 시 5V, 400mA이하로 사용해야 한다. 만일 이를 어길 경우 PC 또는 노트북의 USB포트가 망가질 수 있으므로 각별한 주의가 필요하다.

### 2.제품 사용방법

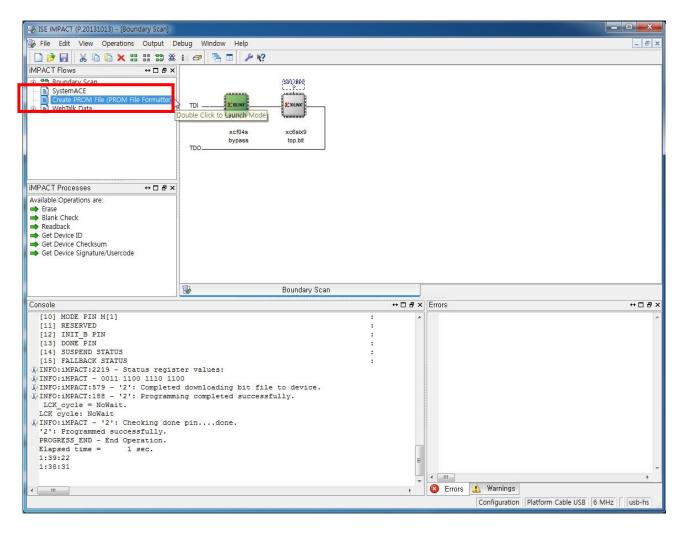

#### 2.1 JTAG Write Mode

FPGA 내부 SRAM 메모리에 직접 프로그램 bit파일을 직접 저장하는 방법으로 iMPACT와 ChipScope를 통해 내부 SRAM에 다운로드 하는 방식이다. 위 모드를 사용할 시에는 점퍼를 아래사진과 같이 설정하도록 한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | I K이베디드     |

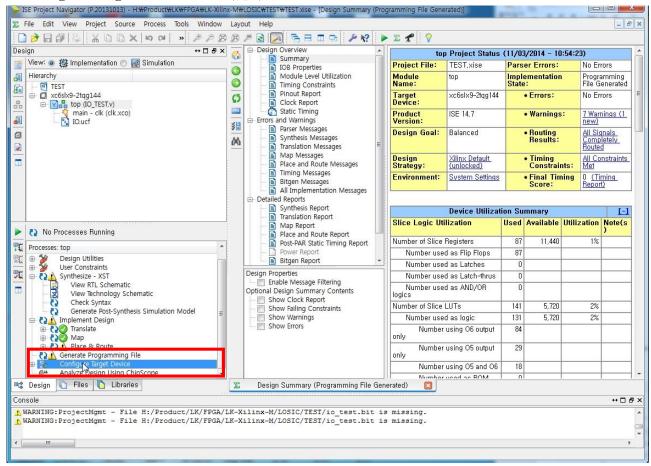

#### 2.2다운로드 실행 과정

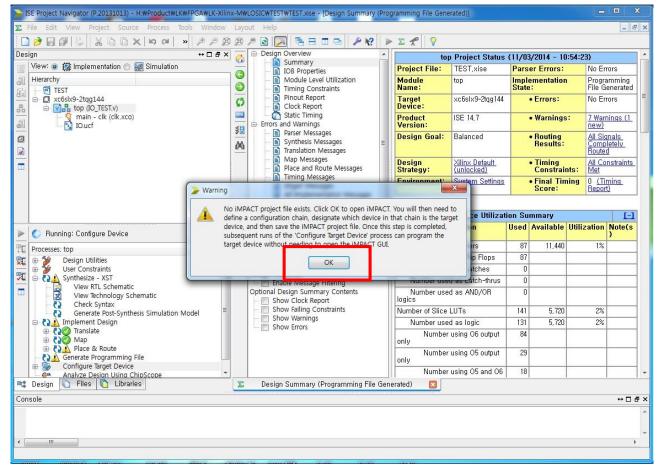

1) Generate Programming File을 더블 클릭하여 bit 파일을 생성한다. bit 파일 생성 후 아래와 같이 Configure Target Device 를 클릭한다.

TITLE: Education

Revisin V0.1

Status Date 2015/05/25

Doc LK임베디드

### LK-FPGA-XC3 Manual

#### 2) OK 버튼을 클릭한다.

| TITLE: | Е | ducation |             |

|--------|---|----------|-------------|

|        |   | Revisin  | V0.1        |

| Status |   | Date     | 2015 /05/25 |

|        |   | Doc      | I K이베디ㄷ     |

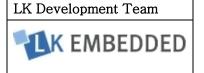

3) Boundary Scan 메뉴를 클릭한다.

| TITLE: E | ducation |             |

|----------|----------|-------------|

|          | Revisin  | V0.1        |

| Status   | Date     | 2015 /05/25 |

|          | Doc      | LK임베디드      |

| LK Development Team |         |  |

|---------------------|---------|--|

| <b>U</b> K E        | MBEDDED |  |

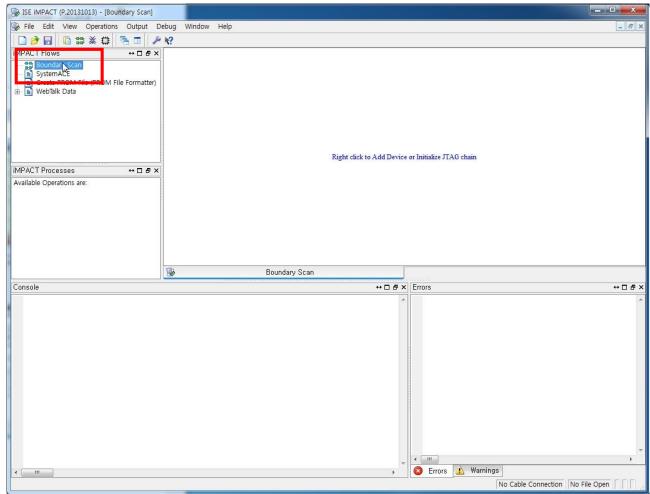

4) Device Programming Properties 에서 Device2 (FPGA XC3S200)를 선택한 후 OK버튼을 클릭한다.

| TITLE: I | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK임베디드      |

| LK Development Team |  |  |

|---------------------|--|--|

| K EMBEDDED          |  |  |

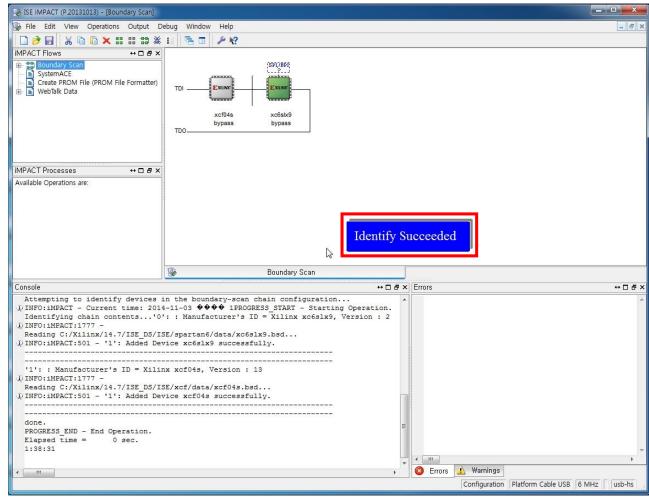

5) Identify Succeeded 메시지를 확인 한다.

| TITLE: E | ducation |             |

|----------|----------|-------------|

|          | Revisin  | V0.1        |

| Status   | Date     | 2015 /05/25 |

|          | Doc      | LK임베디드      |

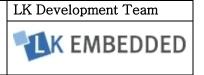

6) XC3S200 FPGA 아이콘을 두 번 클릭 한 후 프로젝트 폴더에 있는 bit파일을 불러온다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | I K이베디드     |

| LK Development Team |  |  |

|---------------------|--|--|

| K EMBEDDED          |  |  |

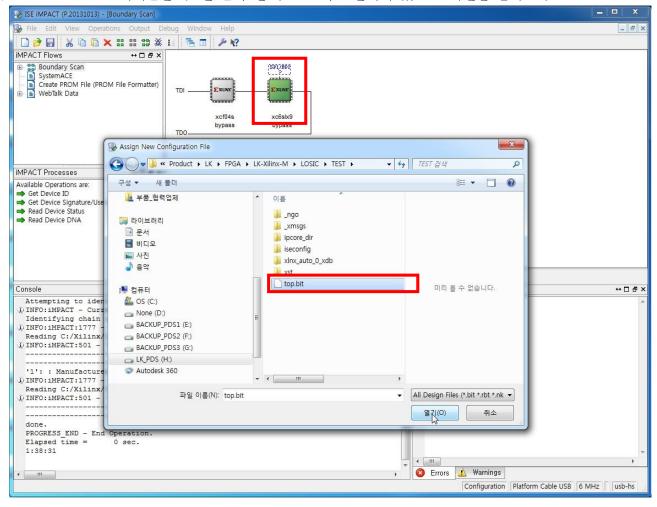

7) bit파일을 불러온 후 Attach SPI or BPI PROM메뉴가 뜬다. 이때 No버튼을 클릭한다.

| TITLE: E | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK임베디드      |

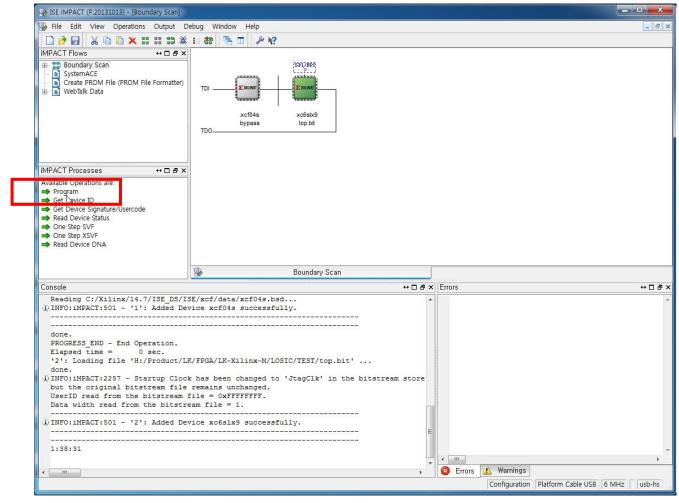

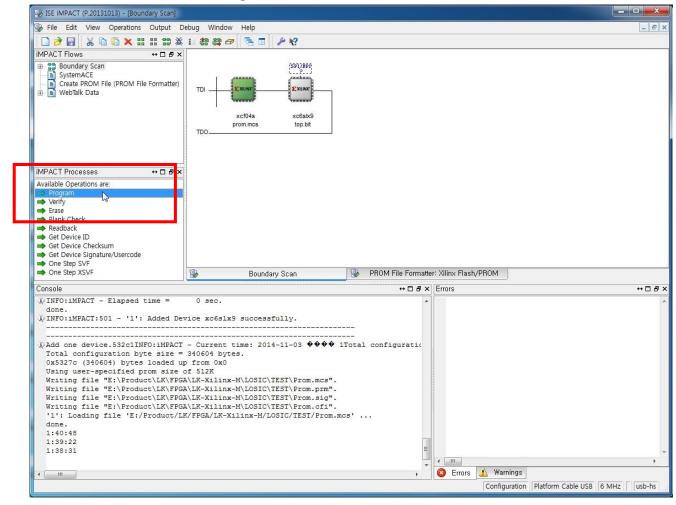

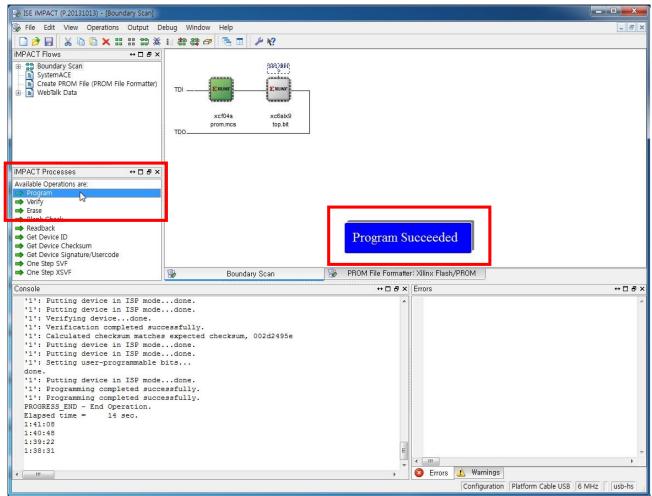

8) bit파일을 불러온 후 IMPACT Processes 창에서 Program 화살표를 클릭한다.

| TITLE: 1 | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK이베디드      |

| LK Development Team |

|---------------------|

| K EMBEDDED          |

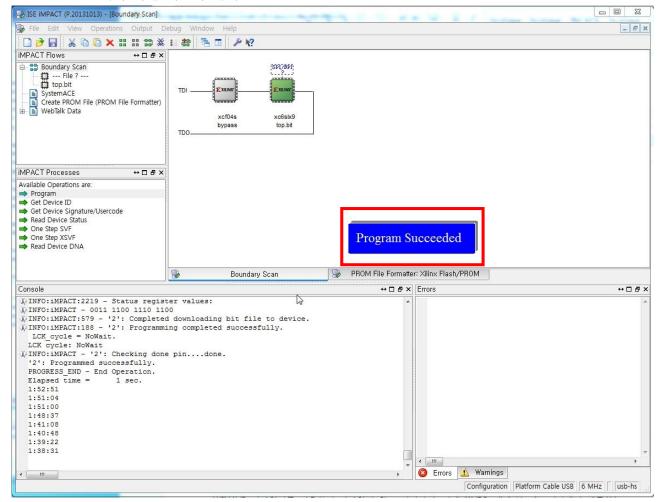

9) Program 화살표를 클릭 후 아래와 같이 Program Succeeded 메시지를 확인 후 FPGA 구동여부를 FPGA 보드에서 확인 하도록 한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Dog       | T K이베니드     |

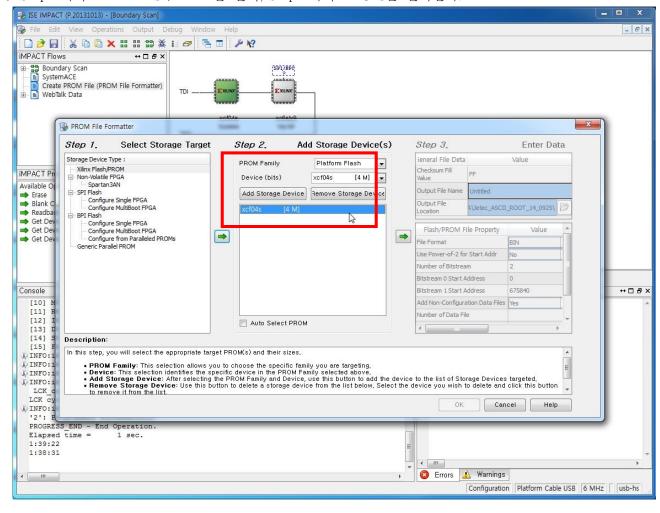

#### 2.3 PROM Write Mode

FPGA 내부 SRAM 메모리에 직접 프로그램 하는 방법이 아닌 자일링스사에 PROM에 bit파일을 직접 저장하는 방법으로 iMPACT와 ChipScope를 통해 PROM에 다운로드 하는 방법이다. 즉, 파워를 ON 시킬 때마다 다운로드 해야 하는 번거로움을 해소하기 위하여 PROM에 다운로드 데이터를 저장시켜놓고 파워를 ON 시킬 때 마다 자동으로 다운로드 하는 방식이다.

위 모드를 사용할 시에는 점퍼를 아래사진과 같이 설정하도록 한다.

| TITLE: 1 | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK임베디드      |

#### 2.4 다운로드 실행 과정

1) Create PROM File 을 클릭한다.

| TITLE: | Е | ducation |             |

|--------|---|----------|-------------|

|        |   | Revisin  | V0.1        |

| Status |   | Date     | 2015 /05/25 |

|        |   | Doc      | I K이베디ㄷ     |

| LK Development Team |

|---------------------|

| K EMBEDDED          |

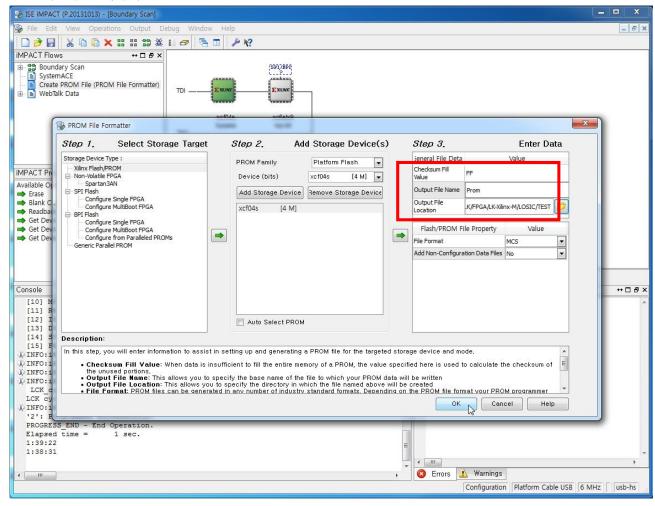

2) Step 1에서 Xilinx Flash/PROM을 선택, Step 2에서 xcf04s를 선택한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | IK이베디드      |

3) Step2까지 설정을 마친 후 화살표를 눌러 Step 3로 진행한다. Step3에서는 Output File Name이름을 다. 이름입력 후 출력파일 위치 디렉토리 설정도 하도록 한다. 아래 예제에서는 Prom이라고 작성 후, OK 버튼을 클릭한다.

| TITLE: 1 | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK이베디드      |

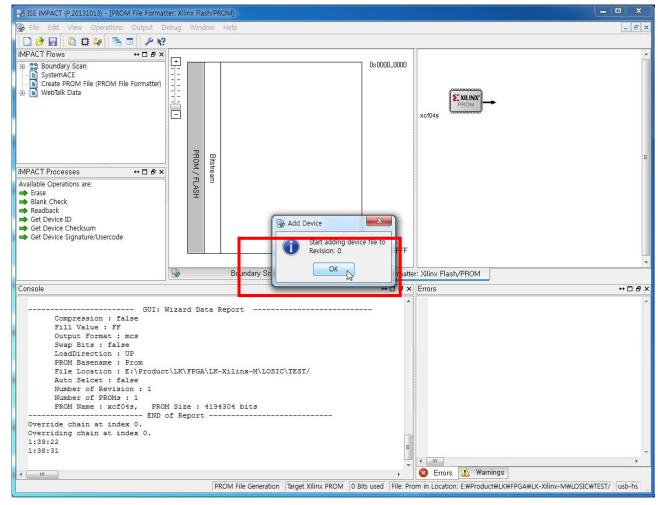

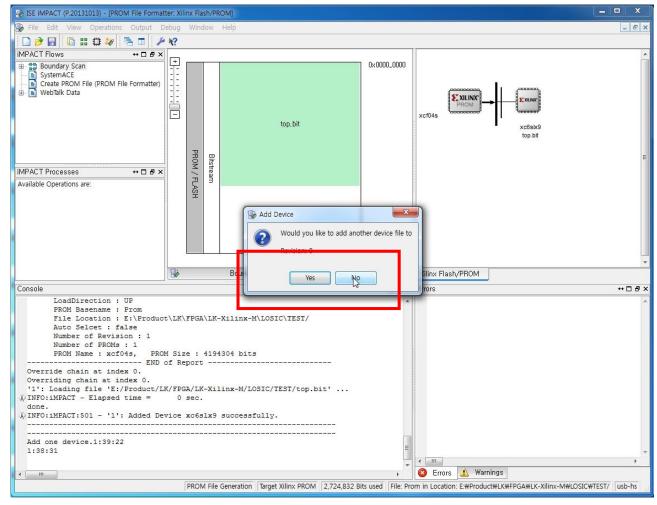

4) 위 그림 4.3순서를 마친 후 아래와 같이 Add Device 메뉴가 뜬다. 이때에 OK버튼을 클릭한다.

| TITLE: H | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK임베디드      |

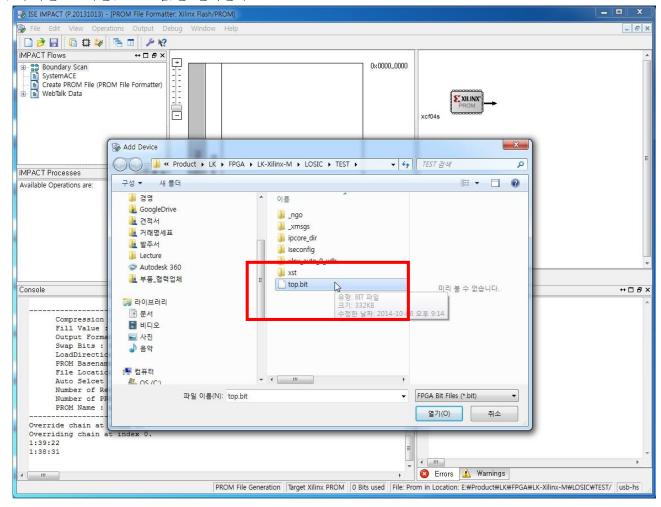

5) 추가할 bit 파일(프로그램)을 선택한다.

2015 LK EMBEDDED

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | I K이베디ㄷ     |

6) bit 파일(프로그램)을 선택 후 추가 bit 파일이 있는 지 물어 본다. 이때에는 NO 버튼을 클릭한다.

| TITLE: 1 | Education |             |

|----------|-----------|-------------|

|          | Revisin   | V0.1        |

| Status   | Date      | 2015 /05/25 |

|          | Doc       | LK이베디드      |

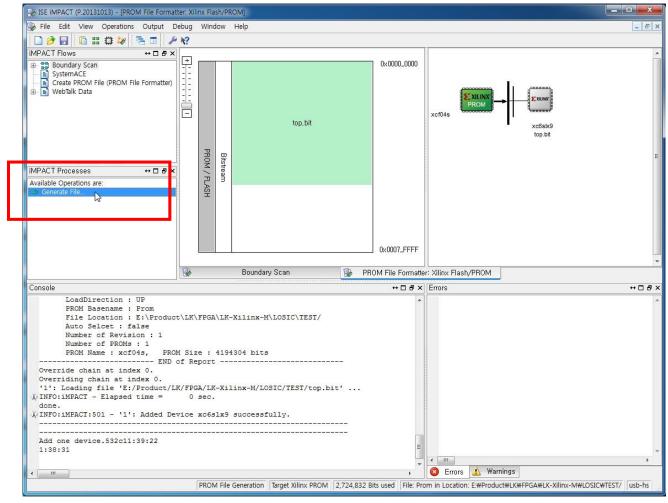

7) MCS 파일(PROM 파일)을 생성하기 위하여 아래와 같이 화살표 Generate File 을 클릭한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | I K이베디드     |

| LK Development Team |

|---------------------|

| K EMBEDDED          |

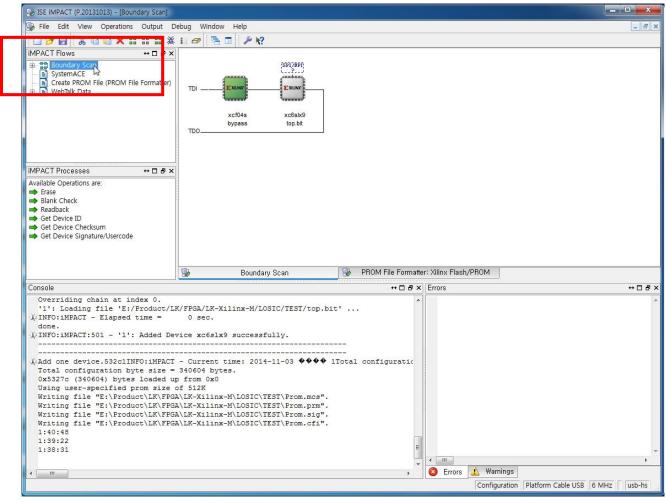

8) Boundary Scan 을 클릭 한 후 xcf04s PROM 을 더블 클릭한다.

| TITLE: E | Education |             |  |

|----------|-----------|-------------|--|

|          | Revisin   | V0.1        |  |

| Status   | Date      | 2015 /05/25 |  |

|          | Doc       | LK임베디드      |  |

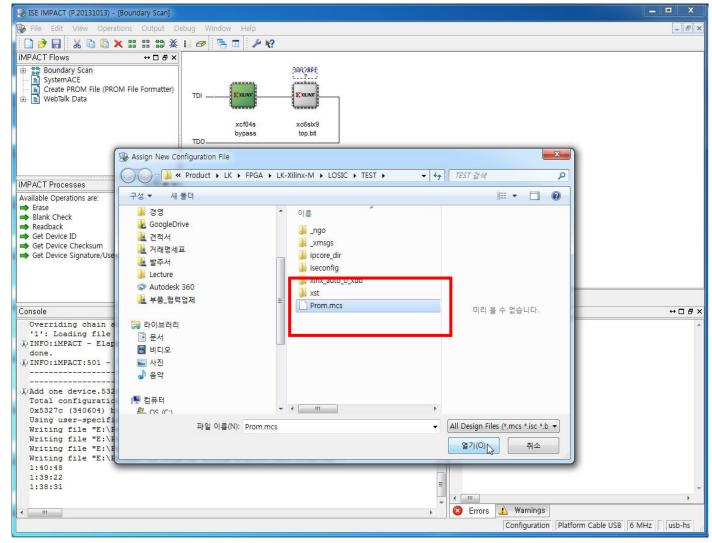

9) PROM 더블 클릭 후 Prom.mcs 파일을 선택한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

|        | Revisin   | V0.1        |

| Status | Date      | 2015 /05/25 |

|        | Doc       | LK임베디드      |

10) MCS 파일 선택 후, 화살표 Program 을 클릭한다.

| TITLE: | Education |             |

|--------|-----------|-------------|

| Status | Revisin   | V0.1        |

|        | Date      | 2015 /05/25 |

|        | Doc       | LK임베디드      |

| LK Development Team |  |  |

|---------------------|--|--|

| *** EMBEDDED        |  |  |

11) Program 화살표를 클릭 후 아래와 같이 "Program Succeeded" 메시지를 확인 후 FPGA 구동여부를 FPGA 보드에서 확인 하도록 한다.

| TITLE: | Education |         |             |

|--------|-----------|---------|-------------|

| Status |           | Revisin | V0.1        |

|        |           | Date    | 2015 /05/25 |

|        |           | Doc     | I K이베디ㄷ     |

### 3.Epilog

#### ✓ 기술지원 및 주의사항

- -LK임베디드홈페이지문의: WWW.LKEMBEDDED.CO.KR상담문의게시판 이용

- -LK임베디드 카페문의: http://cafe.naver.com/lkembedded제품Q&A게시판 이용

- -엔지니어 이메일 기술문의: LKN9270@lkembedded.co.kr

- -엔지니어 기술상담 전화문의: Tel. 02-968-8616~7

- LK임베디드 모든 제품에 DC전원 입력 시 반드시 극성(+,-)를 확인 하시여 전원을 공급해주시고, 제품 정격전압을 꼭 지켜 주셔야 합니다. 만일 이를 어길 시에는 제품에 치명적인 오류 및 파손이 발생할 수 있으니 각별한 주의가 필요합니다.

#### ✓ 감사의 글

LK임베디드 제품을 구입해 주셔서 감사합니다. 당사는AVR, PIC, ARM(STM32F103)을 사용하시는 고객님의 편의를 증진시키기 위해서, 마이컴 교육 및 신제품 연구개발을 위해서 항상 노력하고 있습니다. 앞으로도 끊임없는 도전정신을 바탕으로 신제품개발, 완벽한 품질보증 체계확립, 대 고객 서비스를 통해고객의 마음을 편하게 하는데 정진할 것입니다.

본 제품을 활용하여 마이컴 학습 및 제품개발에 큰 도움 되시기를 바랍니다.